# Terminal optimization analysis for functional block re-use

Stephen E. Krufka Phillip Christie University of Delaware Newark, DE 19716

#### Introduction

- Aid the designer in designing a SoC chip to optimize wire length on the chip.

- Improve clock rate and/or decrease power loss of the chip.

- Provide a mathematical model which can be used to chose between two methods of design.

#### **Description of SoC Chips**

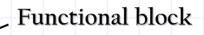

- Increasing trend towards re-use of large functional blocks

- Like a printed circuit board, pre-built functional blocks are mounted on the chip

- Analysis on functional block placement has not yet been done.

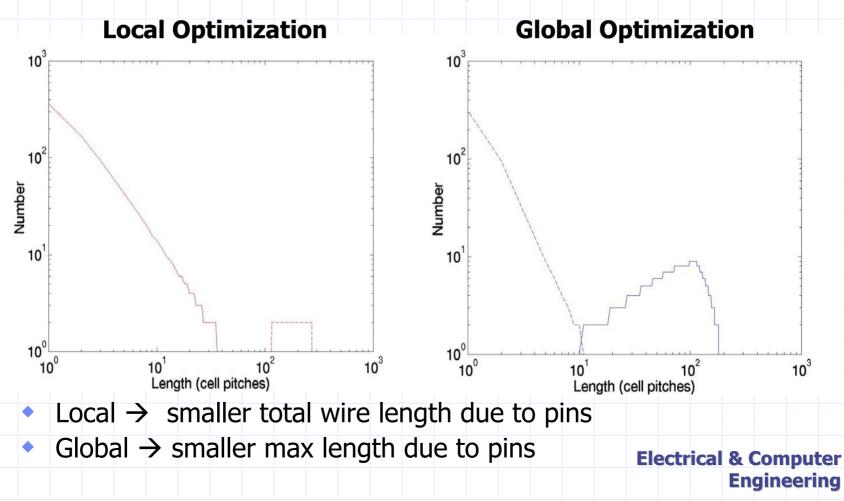

#### Local and Global optimization

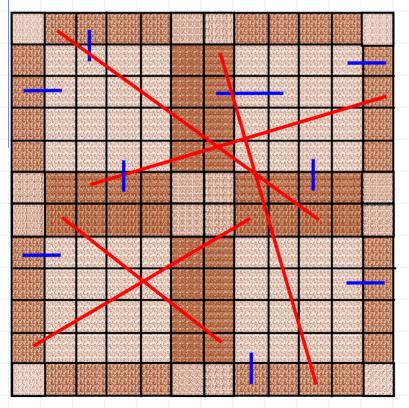

Pins may be placed to optimize either global or local wire lengths.

#### **Local Optimization**

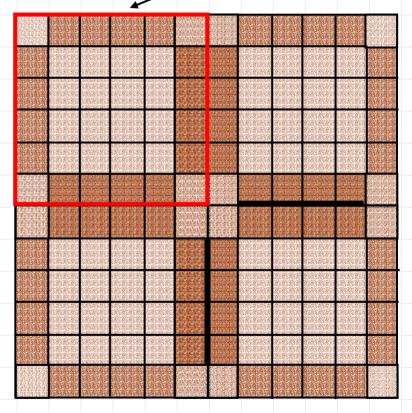

**Global Optimization**

#### Mathematical Model

- Analysis is based on wire length distribution

- Function to find the number of wires of length l

## N(l) = q(l) D(l)

### D(l) = Number of placement sites

### q(l) = Pr{placement site is filled}

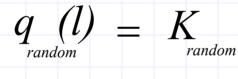

#### Probability function q(1)

- Two forms of probability used in model

- For random placement of pins

- For optimized placement of pins

$$q_{optimized}(l) = K_{opt} l^{-(4-2p)}$$

• In both cases,  $K_{opt}$  and  $K_{random}$  can be found by ensuring

Total number of terminal connected wires  $= \sum N(l)$

L max 1 = 1

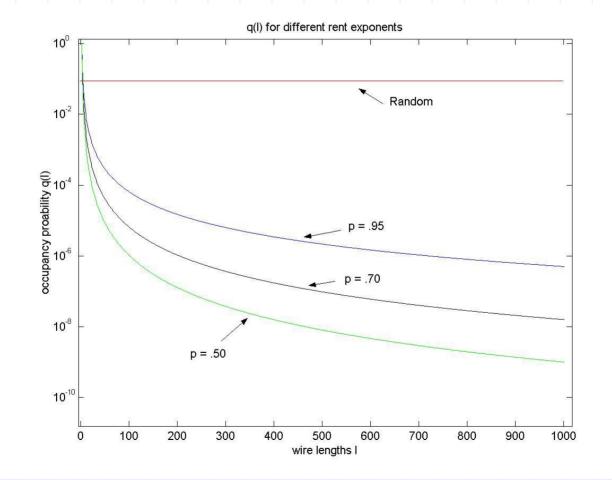

#### q(I) and the Rent Exponent

#### Sites function *D(I)* for local wires

Derived by the method of generating polynomials

#### Sites function for global wires

Can use these three site functions to construct other, higher-level site functions.

C

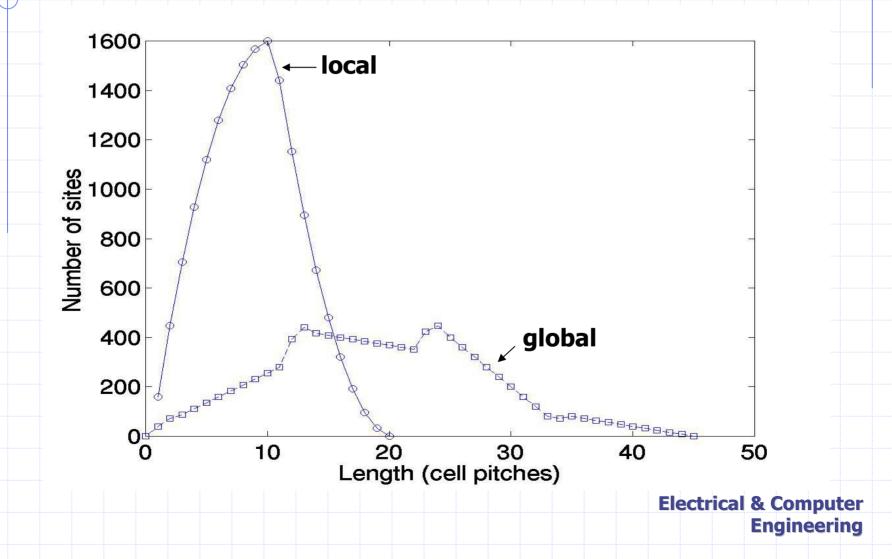

#### Plot of local and global site functions

#### Floor Plan Analysis

- Model both case

- Local Optimization

$$N_{local}^{opt}(l) = q_{opt}(l) D_{local}(l)$$

$$N_{global}^{random}(l) = q_{random}(l) D_{global}(l)$$

Global Optimization

$$N_{local}^{random}(l) = q_{random}(l) D_{local}(l)$$

$$N_{global}^{opt}(l) = q_{opt}(l) D_{global}(l)$$

#### Finding total Wire length

- The length distribution is used to calculate the total wire length due to pins connected nets

- Same equation is used for local or global optimization

Total Wire Length =

$$\sum_{l=1}^{L_{max}} l N_{local}(l) + \sum_{l=1}^{L_{max}} l N_{global}(l)$$

Compare results for local and global optimization to find which method of optimization is better.

## Analysis:

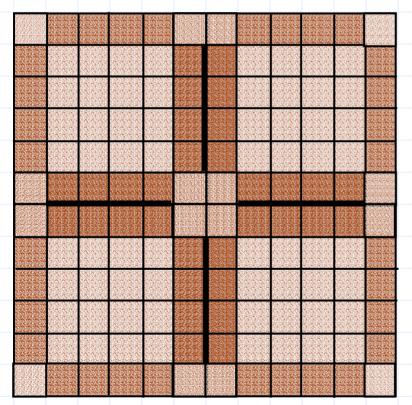

#### Square chip with 4 identical functional blocks

12,769 cells and 245 terminals per functional block

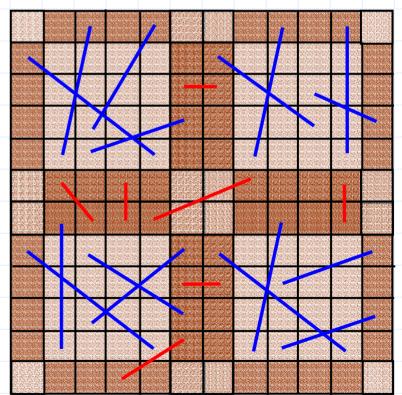

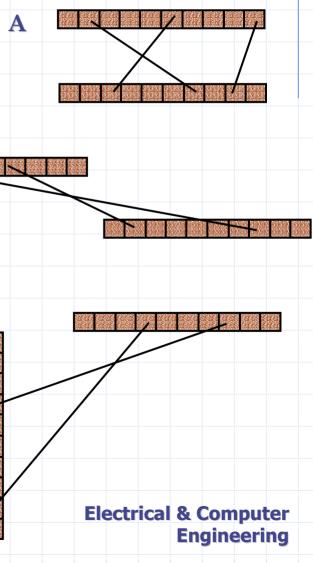

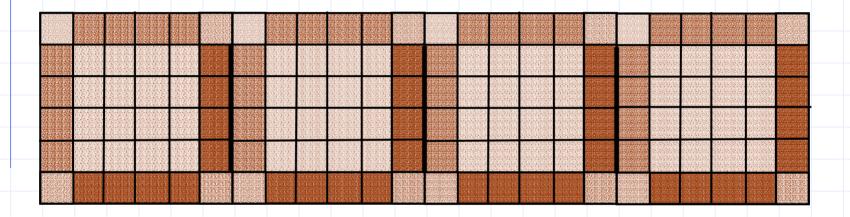

#### Analysis: performed on linear array

Linear array using the same 4 functional blocks as the square arrangement

#### Comparison of results

| Square Floor plan |        |         |         |         |  |  |  |  |  |  |

|-------------------|--------|---------|---------|---------|--|--|--|--|--|--|

| Optimization      | Local  | Global  | Total   | Maximum |  |  |  |  |  |  |

| Strategy          | Length | Length  | Length  | Length  |  |  |  |  |  |  |

| Local             | 5,645  | 85,488  | 91,113  | 333     |  |  |  |  |  |  |

| Global            | 92,580 | 901     | 93,481  | 199     |  |  |  |  |  |  |

| Linear Floor plan |        |         |         |         |  |  |  |  |  |  |

| Optimization      | Local  | Global  | Total   | Maximum |  |  |  |  |  |  |

| Strategy          | Length | Length  | Length  | Length  |  |  |  |  |  |  |

| Local             | 5,645  | 104,598 | 110,243 | 428     |  |  |  |  |  |  |

| Global            | 92,580 | 1,080   | 93,660  | 199     |  |  |  |  |  |  |

- Global optimization yields smaller total wire length and a smaller maximum wire length

- Square floor plan produced less wire then linear

#### Conclusions

- The choice between optimizing local and global wires depends on the geometry of the chip.

- By deriving three basic site functions for global wires, the global site function for higher level designs can be realized as a linear combination of these basic site functions.

- A model has been shown to aid in the decision between optimizing global or local wire length to decrease the total wire length.

#### Acknowledgements

- Advisor

- Prof. Phillip Christie (University of Delaware)

- Financial Support

- National Science Foundation

- Grant No. CCR-9872159