### Getting more out of Donath's hierarchical model for interconnect prediction

J. Dambre, P. Verplaetse, D. Stroobandt and J. Van Campenhout, Ghent University, Electronics and Information Systems Department

## Presentation outline

- Introduction: Donath's technique

- The gap towards modeling real circuit placements

- Closing (part of) the gap

- Placement based on bipartitioning

- From Rent's rule to the Rent characteristic

- Relaxing layout medium size and circuit size

- Impact of rectangular layout grids and cell shapes

- Conclusions

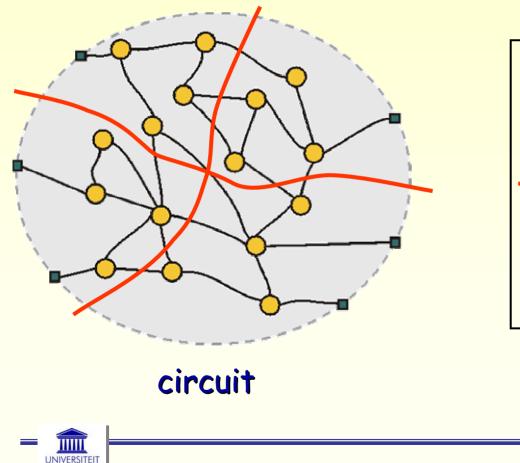

### Donath's placement model: circuit model

Circuit netlist, consists of:

- 4<sup>K</sup> gates

- Connections between gates (internal nets)

- Connections to circuit's exterior (external nets)

Only two-terminal connections considered !

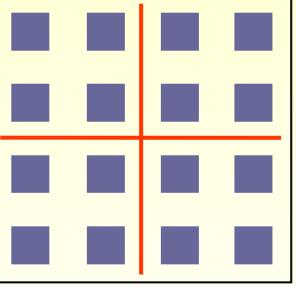

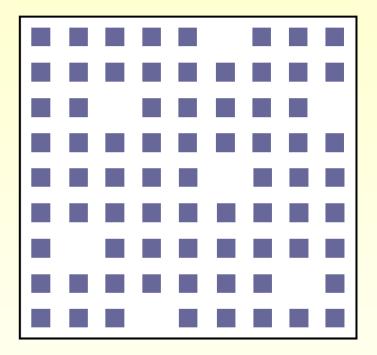

### Donath's placement model: architecture model

#### Architecture consists of:

- square grid of  $2^{\kappa} \times 2^{\kappa}$  possible gate locations

- Manhattan distance metric: length = x-distance + y-distance

- with equal unit distances in both directions

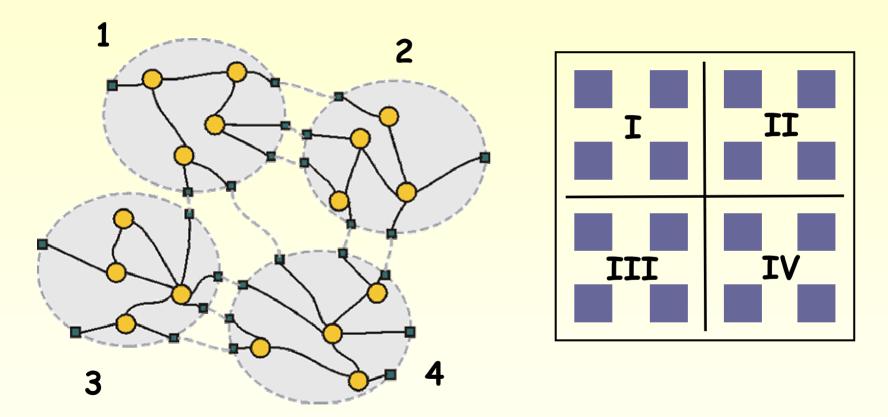

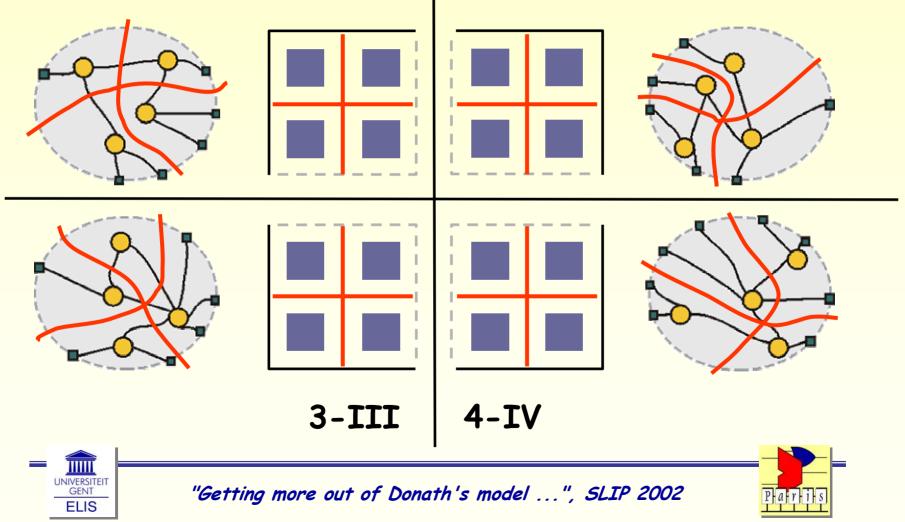

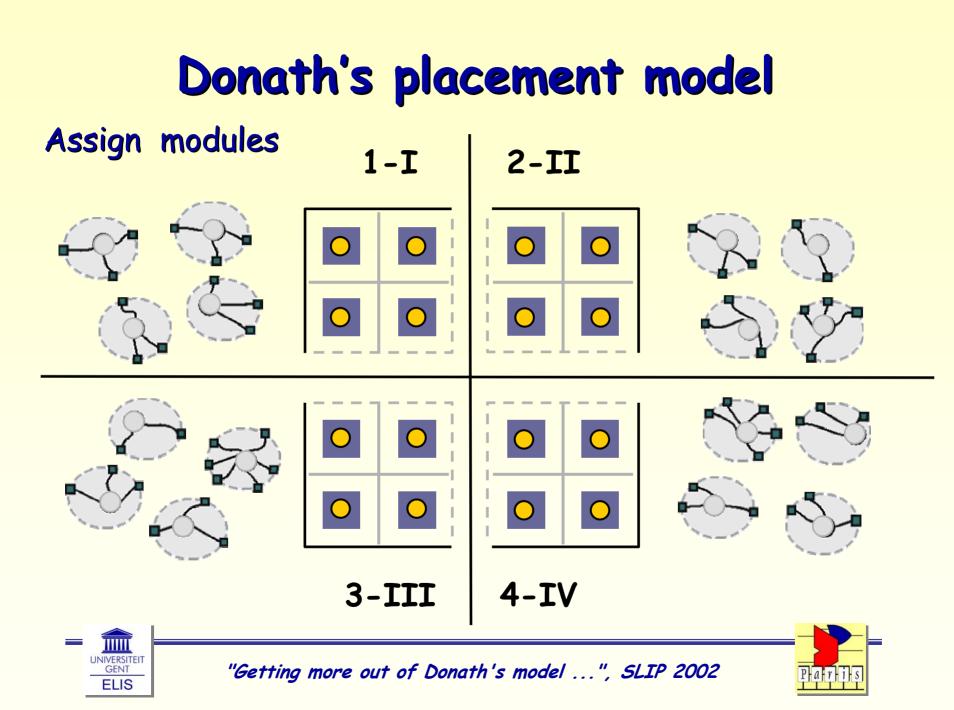

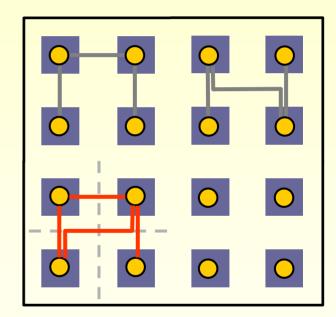

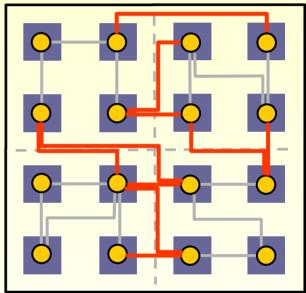

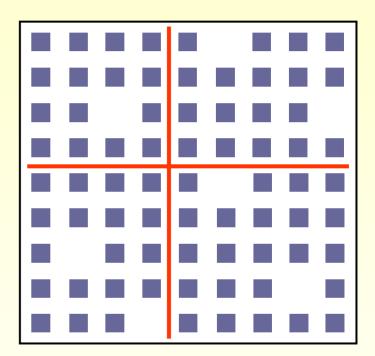

### **Donath's placement model** Perform 4-way partitioning of circuit and architecture

GENT

#### architecture

Randomly assign circuit modules to architecture modules

# Donath's placement model Partition modules 1-I 2-II

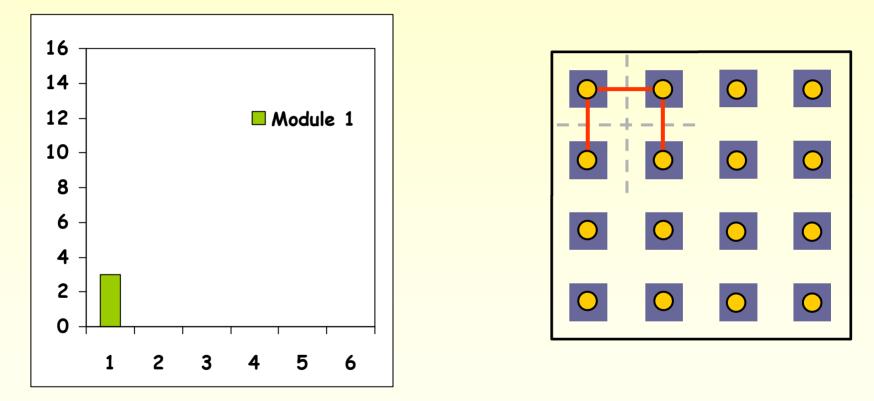

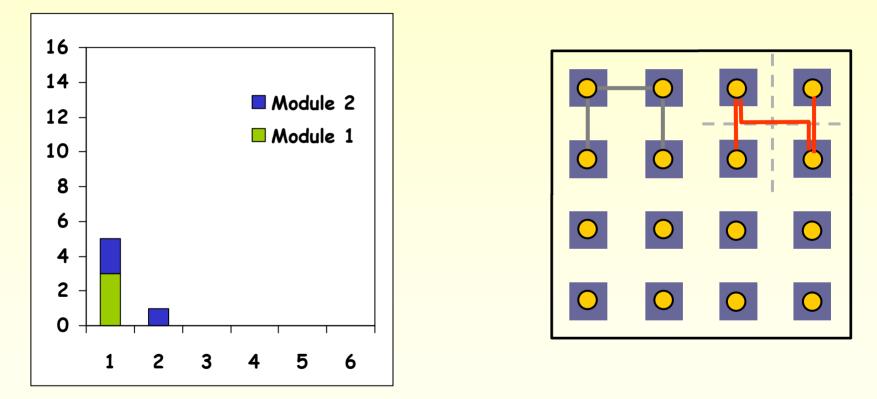

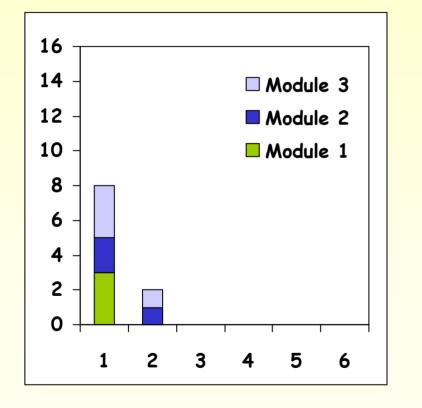

Count number of nets of each length (for every partitioned module):

Count number of nets of each length (for every partitioned module):

Count number of nets of each length (for every partitioned module):

Count number of nets of each length (for every partitioned module):

Count number of nets of each length (for every partitioned module):

Count number of nets of each length (for every partitioned module):

Only lengths of internal wires Only minimal routing distance

## Donath's wirelength distribution estimation technique

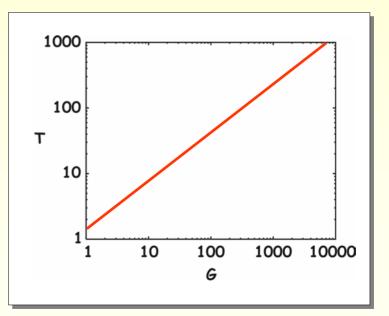

Number of nets that is cut at each level derived from Rent's rule:

p: Rent exponent t: Rent coefficient

- Empirical formula

- Relates the average number of terminals T coming out of a circuit module to the average number of gates G in that module

### Donath's wirelength distribution estimation technique

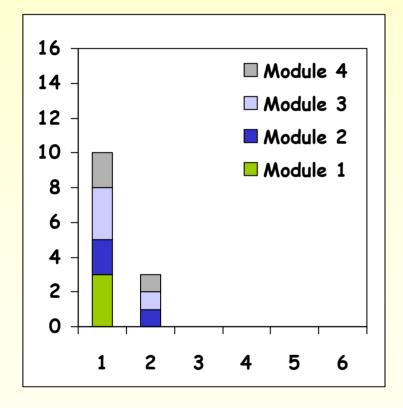

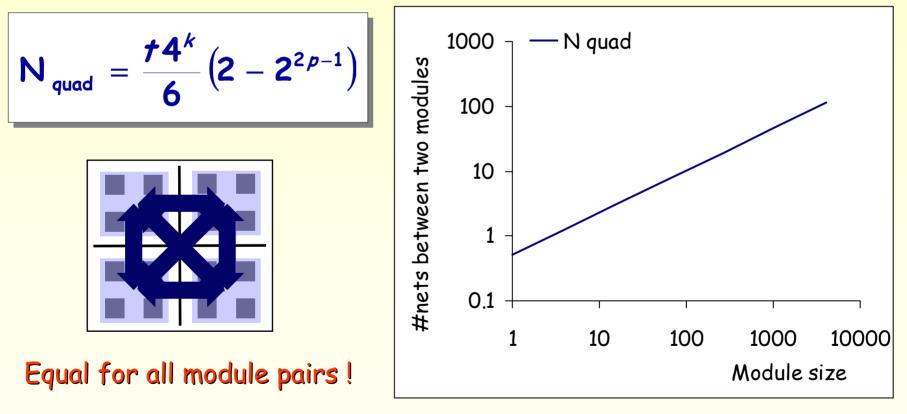

Number of nets connecting each module pair (p=0.65, t=4):

## Donath's wirelength distribution estimation technique

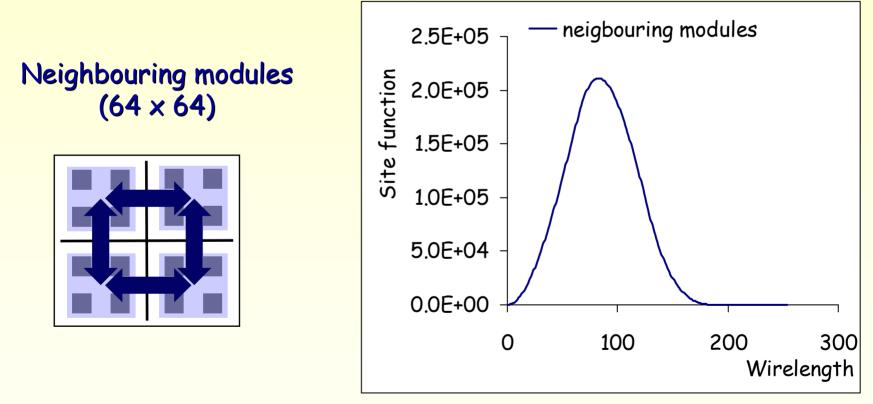

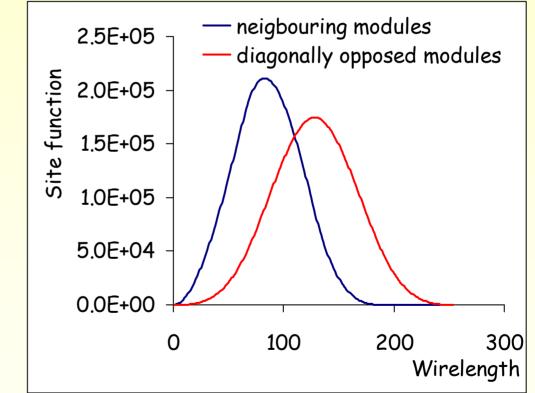

Length distribution of nets connecting each module pair : random terminal positions (sampled from site function)

### Donath's wirelength distribution estimation technique

Length distribution of nets connecting each module pair : random terminal positions (sampled from site function)

Diagonally opposed modules (64 × 64)

## Donath's wirelength distribution estimation technique

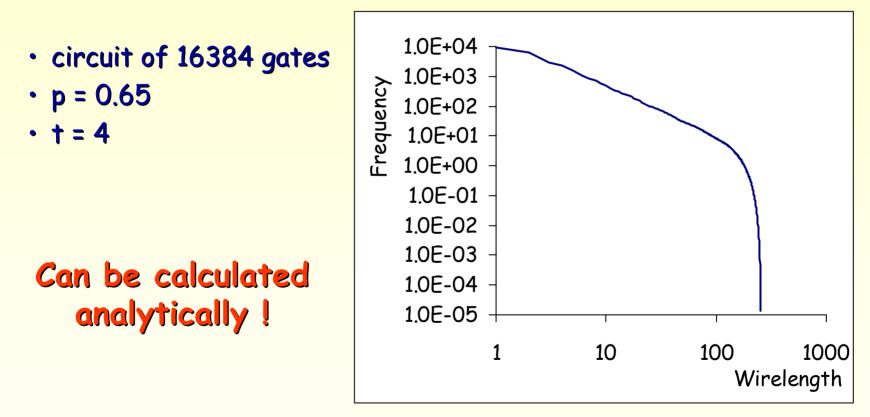

Total wirelength distribution for:

## Underlying assumptions in Donath's model

- 1. Rent's rule applies for all module sizes

- 2. Number of gates =4<sup>k</sup> and equals architecture grid size

- 3. Architecture is square grid with square cells

- 4. Placement based on hierarchical 4-way partitioning

- 5. Only optimization during placement: minimization of number of nets cut during partitioning

## Evaluation of Donath's placement model

#### All assumptions matched:

- 1. Synthetic benchmark circuits (gnl) with 4<sup>7</sup>=16384 gates that follow Rent's rule almost exactly

- 2. Mapped onto square grid architecture with 4<sup>7</sup> square cells by Donath's placement procedure

#### High variance due to random module assignment: statistical average taken over 500 placement runs

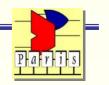

## Evaluation of Donath's placement model

Wirelength distribution for:

- circuit of 16384 gates

- p = 0.65

- **†** = **4**

- 500 placement runs

## Evaluation of Donath's placement model

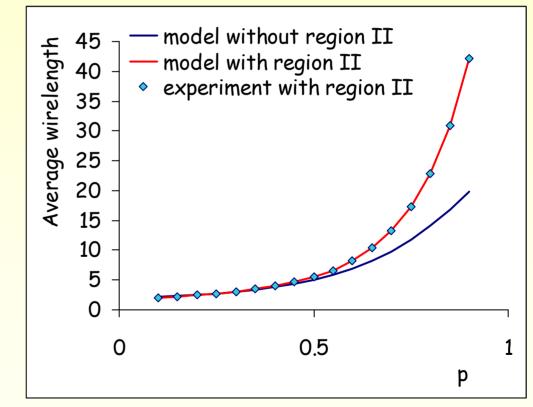

#### Average wirelength for:

• circuits of 16384 gates • p from  $0.1 \rightarrow 0.9$ • t = 4 • 500 placement runs 1.5E+01 - 0.9E+00 - 0.5

"Getting more out of Donath's model ...", SLIP 2002

р

## **Presentation outline**

- Introduction: Donath's technique

- The gap towards modeling real circuit placements

- Closing (part of) the gap

- Placement based on bipartitioning

- From Rent's rule to the Rent characteristic

- Relaxing layout medium size and circuit size

- Impact of rectangular layout grids and cell shapes

- Conclusions

| Donath's method                    | Real placements |

|------------------------------------|-----------------|

| Rent's rule                        |                 |

| Gates = 4 <sup>k</sup> = grid size |                 |

| Square grid with square cells      |                 |

| 4-way partitioning based placement |                 |

| No optimization                    |                 |

| Donath's method                    | Real placements                 |

|------------------------------------|---------------------------------|

| Rent's rule                        | Deviations: Rent characteristic |

| Gates = 4 <sup>k</sup> = grid size |                                 |

| Square grid with square cells      |                                 |

| 4-way partitioning based placement |                                 |

| No optimization                    |                                 |

| Donath's method                    | Real placements                      |

|------------------------------------|--------------------------------------|

| Rent's rule                        | Deviations: Rent characteristic      |

| Gates = 4 <sup>k</sup> = grid size | Gates != 4 <sup>K</sup> != grid size |

| Square grid with square cells      |                                      |

| 4-way partitioning based placement |                                      |

| No optimization                    |                                      |

| Donath's method                    | Real placements                                       |

|------------------------------------|-------------------------------------------------------|

| Rent's rule                        | Deviations: Rent characteristic                       |

| Gates = 4 <sup>k</sup> = grid size | Gates != 4 <sup>k</sup> != grid size                  |

| Square grid with square cells      | Possibly rectangular grid<br>and/or rectangular cells |

| 4-way partitioning based placement |                                                       |

| No optimization                    |                                                       |

| Donath's method                    | Real placements                                       |

|------------------------------------|-------------------------------------------------------|

| Rent's rule                        | Deviations: Rent characteristic                       |

| Gates = 4 <sup>k</sup> = grid size | Gates != 4 <sup>k</sup> != grid size                  |

| Square grid with square cells      | Possibly rectangular grid<br>and/or rectangular cells |

| 4-way partitioning based placement | Often bipartitioning based placement                  |

| No optimization                    |                                                       |

|              | Donath's method                    | Real placements                                       |

|--------------|------------------------------------|-------------------------------------------------------|

|              | Rent's rule                        | Deviations: Rent characteristic                       |

|              | Gates = 4 <sup>k</sup> = grid size | Gates != 4 <sup>k</sup> != grid size                  |

| $\mathbf{I}$ | Square grid with square cells      | Possibly rectangular grid<br>and/or rectangular cells |

|              | 4-way partitioning based placement | Often bipartitioning based placement                  |

|              | No optimization                    | Lots of optimization                                  |

#### Addressed by other authors

## Presentation outline

- Introduction: Donath's technique

- The gap towards modeling real circuit placements

- Closing (part of) the gap

- Placement based on bipartitioning

- From Rent's rule to the Rent characteristic

- Relaxing layout medium size and circuit size

- Impact of rectangular layout grids and cell shapes

- Conclusions

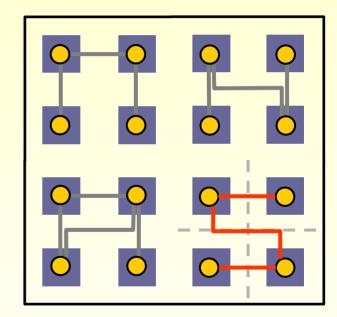

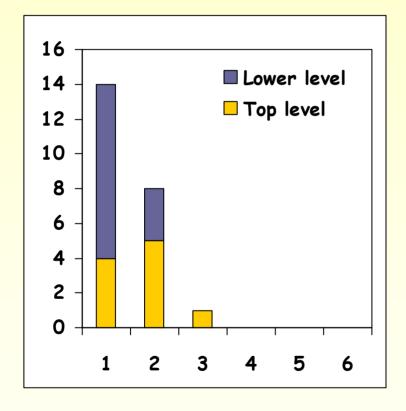

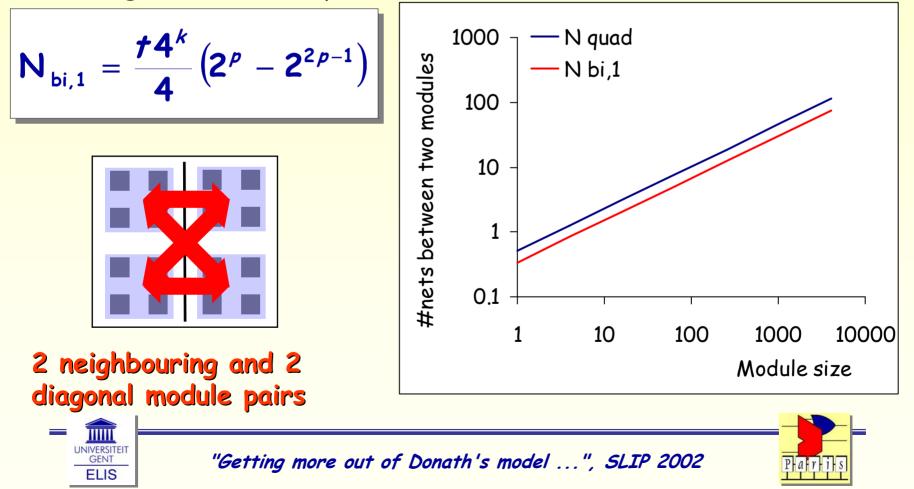

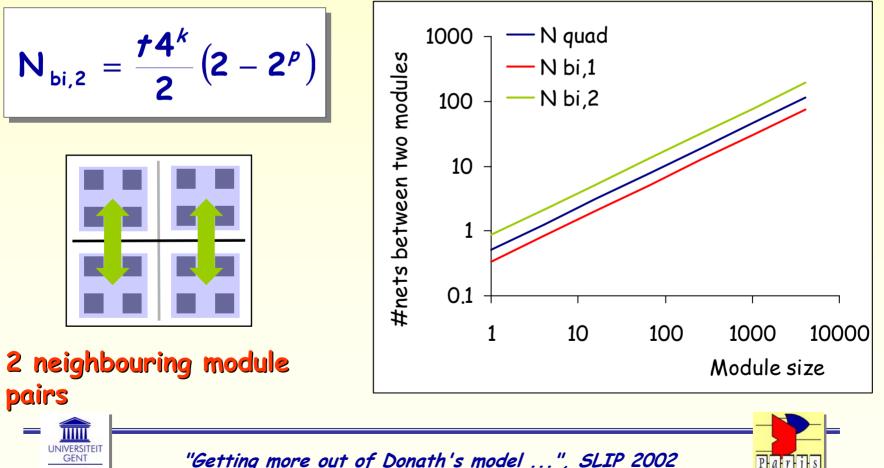

Number of nets connecting each module pair that is separated during the first cut (p=0.65, t=4):

Number of nets connecting each module pair that is separated during the second cut (p=0.65, t=4):

ELIS

## Wirelength distribution corresponding to one hierarchy level for:

- $\cdot$  modules of 64 x 64

- p = 0.65

- **†** = **4**

Total wirelength distribution for:

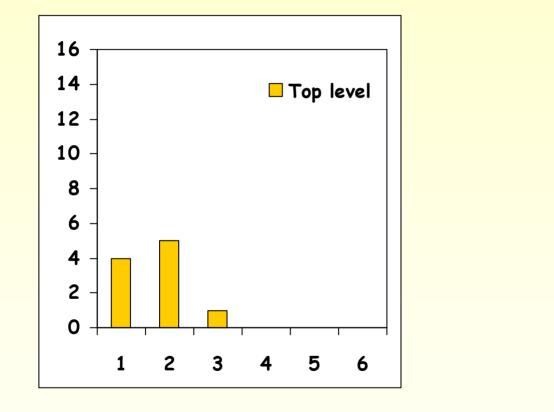

#### Average wirelength for:

- circuits of 16384 gates

- p from 0.1 -> 0.9

- **† = 4**

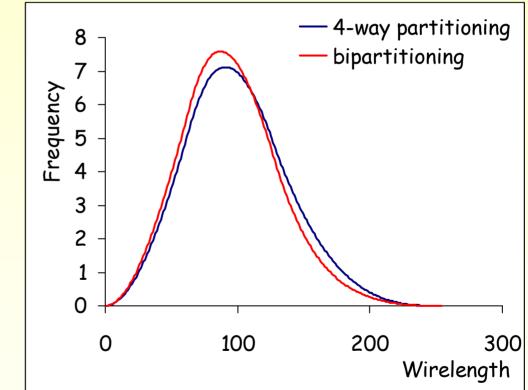

## Bipartitioning vs. 4-way partitioning

Relative difference between average wirelength using 4-way and bipartitioning for:

circuits of 16384 gates % difference • p from 0.1 -> 0.9 -6 • **†** = **4** -8 -10 0 0.5 р

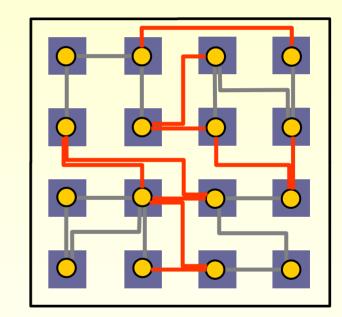

# Bipartitioning vs. 4-way partitioning: validation

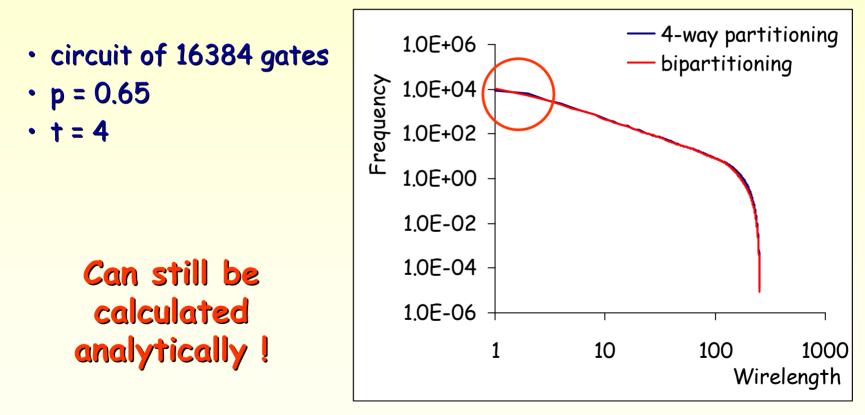

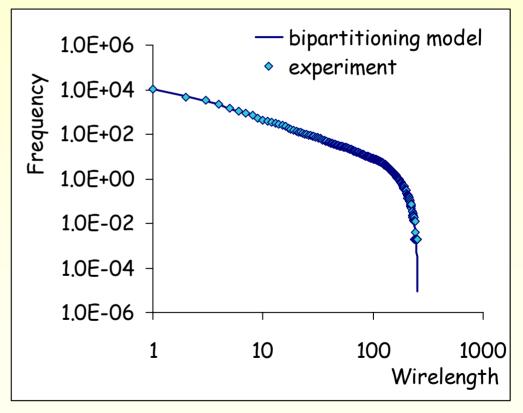

Wirelength distribution for:

- circuit of 16384 gates

- p = 0.65

- **†** = **4**

- 500 placement runs

### Bipartitioning vs. 4-way partitioning: validation

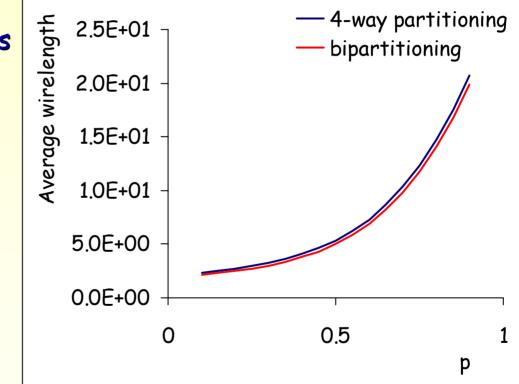

Average wirelength for:

bipartitioning model Average wirelength 2.5E+01 circuits of 16384 gates experiment • p from 0.1 -> 0.9 2.0E+01 • **+ = 4** 1.5E+01 500 placement runs 1.0E+01 5.0E+00 0.0E+00 0.5 0 р

## **Presentation outline**

- Introduction: Donath's technique

- The gap towards modeling real circuit placements

- Closing (part of) the gap

- Placement based on bipartitioning

- From Rent's rule to the Rent characteristic

- Relaxing layout medium size and circuit size

- Impact of rectangular layout grids and cell shapes

- Conclusions

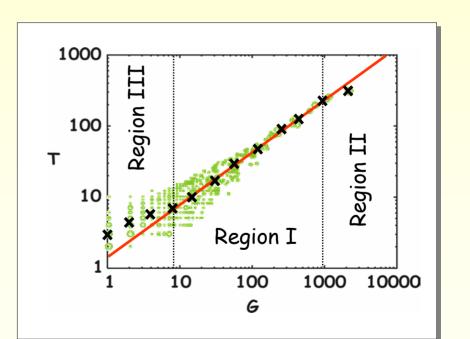

## From Rent's rule to the Rent characteristic

- Derivation of Rent parameters for a given circuit :

- Perform hierarchical circuit partitioning

- Find average data points for T vs. G (=Rent characteristic)

- Fit power law to region I

T = t6<sup>p</sup>

p: Rent exponent t: Rent coefficient

#### From Rent's rule to the Rent characteristic

- Deviations from Rent's rule cause errors in model !

- -> Use Rent characteristic instead

- Not analytical -> numerical model evaluation required

# Impact of region II

#### New synthetic benchmark circuits with same t and p, but with region II

Example for: • p = 0.65 • t = 4

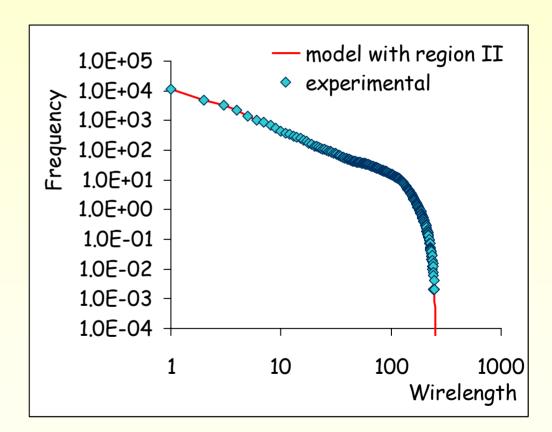

# Impact of region II

#### Wirelength distribution for:

- circuit of 16384 gates

- p = 0.65

- **†** = 4

- bipartitioning based placement

- 500 placement runs

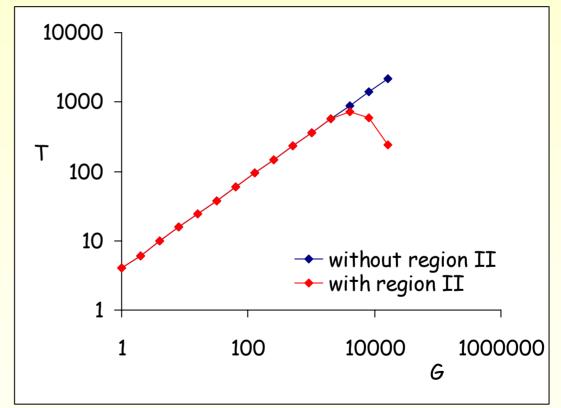

# Impact of region II

#### Average wirelength for:

- circuit of 16384 gates

- p = 0.65

- **† = 4**

- bipartitioning based placement

- 500 placement runs

## **Presentation outline**

- Introduction: Donath's technique

- The gap towards modeling real circuit placements

- Closing (part of) the gap

- Placement based on bipartitioning

- From Rent's rule to the Rent characteristic

- Relaxing layout medium size and circuit size

- Impact of rectangular layout grids and cell shapes

- Conclusions

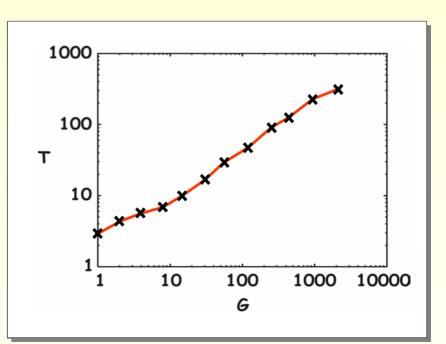

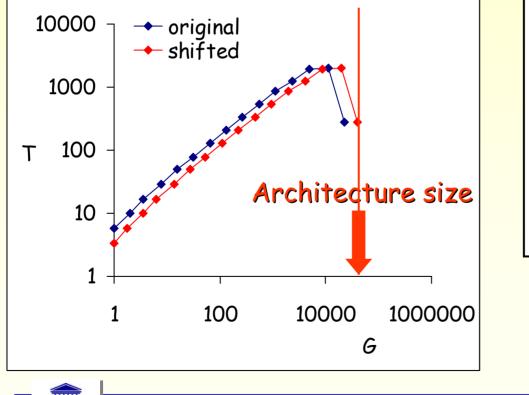

# Circuit size and layout grid size

Number of gates usually different from number of layout grid positions :

- Some empty positions in placement grid

- Suppose homogeneously spread

# Circuit size and layout grid size

Need to 'shift' Rent characteristic Example : ibm03, 57% filling ratio

# Circuit size and layout grid size

Grid side rarely an exact power of 2 :

• Unequal module sizes during architecture partitioning

Impact on model :

- Site functions for rectangles (easy)

- Bipartitioning: no other changes

- 4-way partitioning: suppose number of nets connecting two modules proportional to size of each module

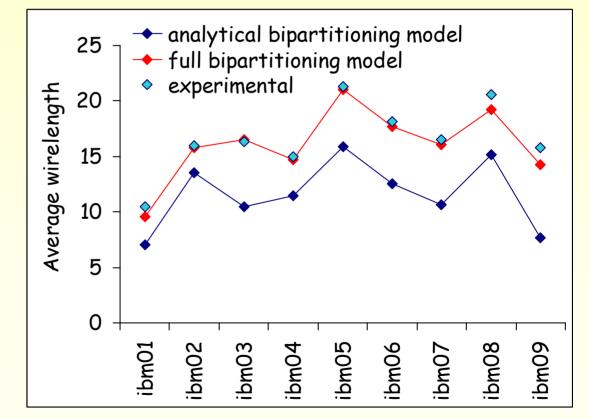

#### And now for some 'real' circuits model compared to unoptimized placement

- benchmarks: ibm01 ibm09

- placed in square grid

- ~ 95 % filled

- using unoptimized bipartitioning based placement (100 runs)

Remaining deviations probably caused by inhomogeneity in circuit complexity

Improved by including Rent's rule variance in model (Verplaetse)?

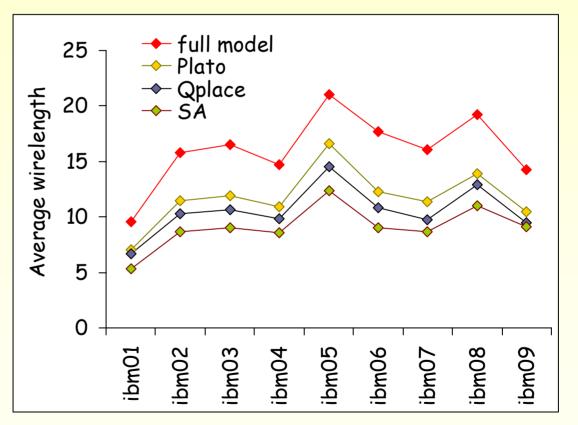

# ... and compared to optimized placement

- benchmarks: ibm01 ibm09

- placed in square grid

- •~ 95 % filled

- using optimized placement :

- Plato (10 runs)

- Qplace (1 run)

- homogeneous SA –

cooling factor 0.999

(1 run)

Overestimation, but very good correlation !

#### **Correlation results**

| Model                     | Unoptimized | optimized |        |            |

|---------------------------|-------------|-----------|--------|------------|

|                           |             | Plato     | Qplace | SA (0.999) |

| Analytical bipartitioning | 0.856       | 0.879     | 0.892  | 0.810      |

| Full<br>bipartitioning    | 0.990       | 0.977     | 0.971  | 0.949      |

Significantly higher correlations with all placement results for full bipartitioning model !

## **Presentation outline**

- Introduction: Donath's technique

- The gap towards modeling real circuit placements

- Closing (part of) the gap

- Placement based on bipartitioning

- From Rent's rule to the Rent characteristic

- Relaxing layout medium size and circuit size

- Impact of rectangular layout grids and cell shapes

- Conclusions

# Rectangular grids ...

Floorplanning: sometimes smaller layout area if rectangular subcircuit layouts allowed

-> change grid aspect ratio

#### Impact on model :

- Site functions for rectangles (easy)

- Partitioning order : choose cut direction to minimize module aspect ratio

# ... and rectangular cells

Cells are often rectangular instead of square : cost in X- and Y-directions different

-> change cell aspect ratio

Impact on model :

- Convert site functions for weighted unit distances (easy)

- Currently only for rational cell aspect ratios !

- Partitioning order : choose cut direction to minimize module aspect ratio

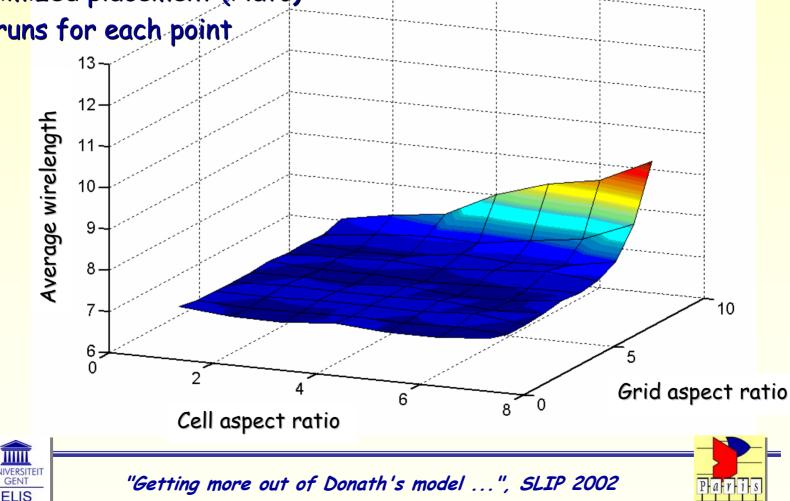

#### Impact of grid and cell aspect ratio

- benchmark ibm01

- optimized placement (Plato)

- 10 runs for each point

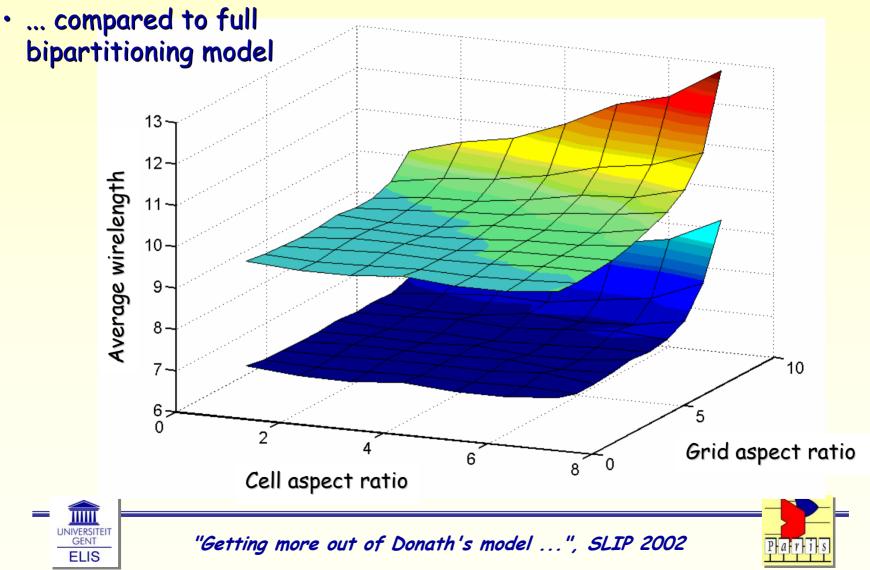

#### Impact of grid and cell aspect ratio

## Impact of grid and cell aspect ratio

Correlations between model and experiment for each benchmark (across 70 architectural variants)

Correlations are very high Model is very suitable for comparing different options

| Benchmark | Correlation |  |  |

|-----------|-------------|--|--|

| ibm01     | 0.964       |  |  |

| ibm02     | 0.990       |  |  |

| ibm03     | 0.999       |  |  |

| ibm04     | 0.987       |  |  |

| ibm05     | 0.998       |  |  |

| ibm06     | 0.979       |  |  |

| ibm07     | 0.992       |  |  |

| ibm08     | 0.994       |  |  |

| ibm09     | 0.998       |  |  |

## **Presentation outline**

- Introduction: Donath's technique

- The gap towards modeling real circuit placements

- Closing (part of) the gap

- Placement based on bipartitioning

- From Rent's rule to the Rent characteristic

- Relaxing layout medium size and circuit size

- Impact of rectangular layout grids and cell shapes

- Conclusions

# Conclusions

Extension of Donath's model to make it accord better with real placement experiments:

- Bipartitioning vs. 4-way partitioning (analytical)

- Use of Partitioning Rent characteristic (region II!)

- Relaxation of circuit and architecture size

- Relaxation of architecture grid and cell aspect ratio

# Conclusions

# Systematic experimental validation, matching assumptions as closely as possible. Results:

- For synthetic (homogeneous) benchmark experiments, models are almost exact (within statistical variation)

- For real benchmarks (unoptimized), some deviations occur, probably due to inhomogeneity of circuit complexity

- Average wirelengths from our models show very high correlation with experimental optimized placement results with different tools

#### And ...

#### the whole thing was implemented in Matlab and is available on request

#### jdambre@elis.rug.ac.be

# Future work

- Include external connections

- Include multi-terminal connections (Stroobandt's models ?)

- Include optimization (tricky !!)