| × |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

The University of New Mexico

# Stochastic Interconnect Layout Sensitivity Model

#### Payman Zarkesh-Ha and Ken Doniger\*

University of New Mexico Department of Electrical and Computer Engineering Albuquerque, NM 87131

\* Abbott Diabetes Care, Alameda, CA 94502

# Outline

- 1. Overview of Process Defects

- 2. Definition of "Layout Sensitivity"

- 3. Statistical Layout Sensitivity Model

- 4. Application in VLSI design/verification process

- 5. Conclusions

# Outline

- 1. Overview of Process Defects

- 2. Definition of "Layout Sensitivity"

- 3. Statistical Layout Sensitivity Model

- 4. Application in VLSI design/verification process

- 5. Conclusions

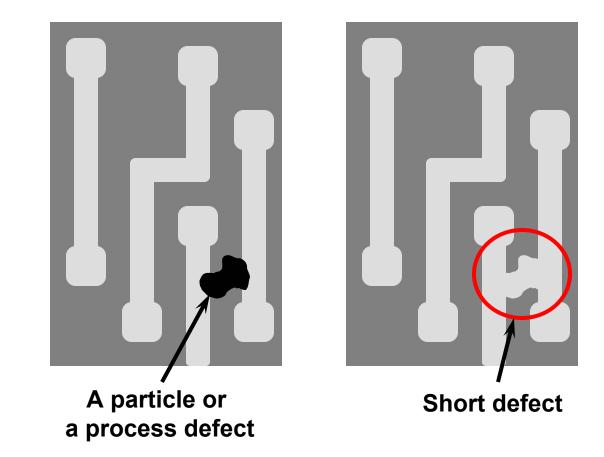

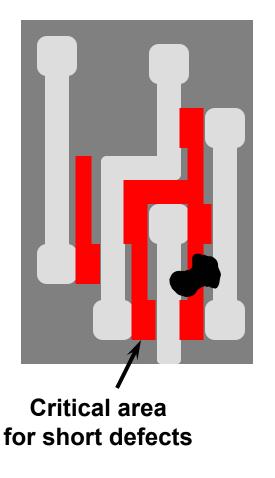

#### **Process Defects and Yield Loss**

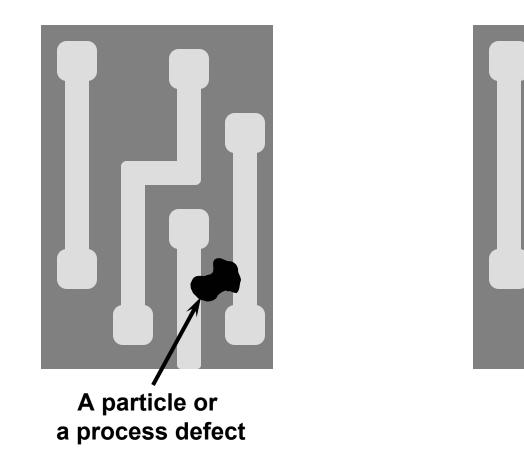

#### Process Defect Causing Fault (Short)

**Original layout**

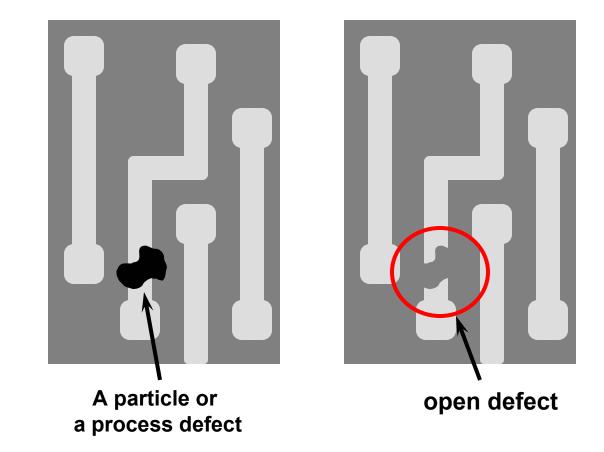

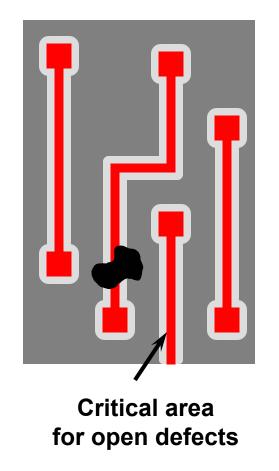

#### **Process Defects and Yield Loss**

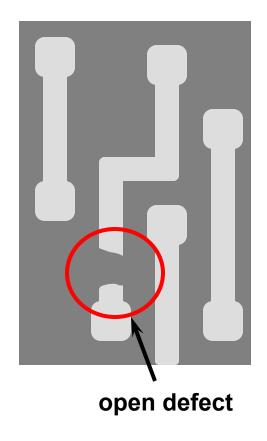

#### Process Defect Causing Fault (Opens)

**Original layout**

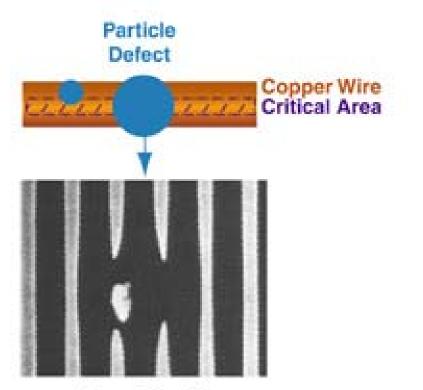

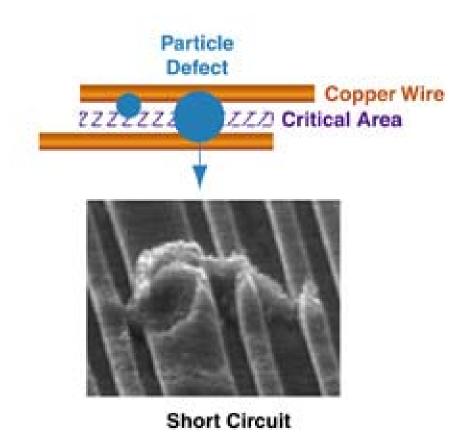

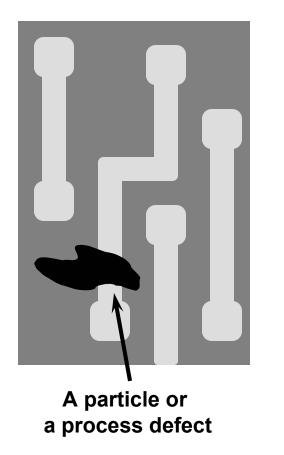

#### **Process Defect Photographs**

**Open Circuit**

# Outline

- 1. Overview of Process Defects

- 2. Definition of "Layout Sensitivity"

- 3. Statistical Layout Sensitivity Model

- 4. Application in VLSI design/verification process

- 5. Conclusions

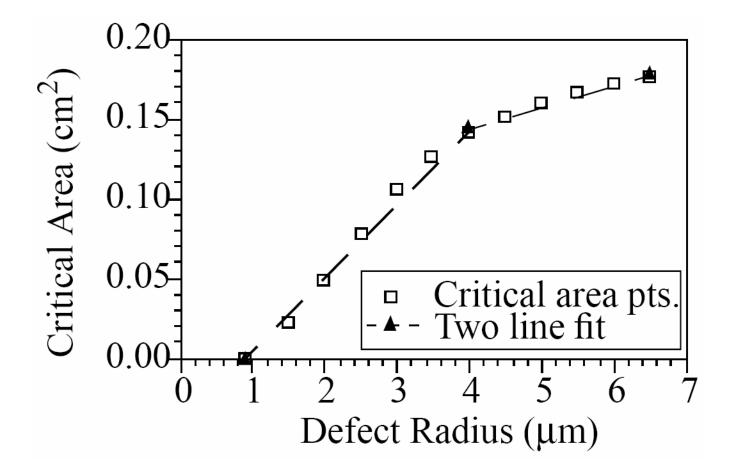

#### **Critical Area and Layout Sensitivity**

#### Short defects

#### Open defects

### What is challenging?

- For yield analysis, layout sensitivity must be calculated for a range of defect sizes.

- Extraction of layout sensitivity in a real chip requires extensive computations, which makes it a very time consuming process.

- Statistical model can expedite the process significantly.

#### **Critical Area Analysis Methods**

- Geometric Methods: Compute the area of critical region for every defect size and for every rectangular element in layout using shape-expansion, shape-overlap, and shape-intersection → needs extensive computation

- Monte Carlo Simulation: Draw a large number of defects with their radii distributed, check for each defect if it causes an failure, and divide the number of defects causing faults by the total number of defects to derive the probability of fault → not accurate with small number of samples

- $\blacktriangleright Stochastic Method:$  Compute layout sensitivity from statistical features of the layout using analytical model  $\rightarrow$  generic but very fast, excellent for prediction

# History Layout Sensitivity

- B. R. Mandava, "Critical area for yield models," IBM, East Fishkill, NY, Tech. Rep. TR22.2436, January <u>1982</u>.

- W. Maly and J. Deszczka, "Yield estimation model for VLSI artwork evaluation," Electron Lett., vol. 19, no. 6, pp. 226–227, March <u>1983</u>.

- A. V. Ferris-Prabhu, "Defect size variations and their effect on the critical area of VLSI devices," IEEE J. Solid-State Circuits, vol. SC-20, pp. 878–880, Aug. <u>1985</u>.

- > .....

- A. Nicoli, "Signoff Evolves From Design-Rule Checking To Yield Analysis," Electronic Design, July 24 <u>2006</u>, http://elecdesign.com/Articles/ArticleID/13132/13132.html

- J. Yan, B. Chiang, "Timing-Constrained Yield-Driven Wiring Reconstruction for Critical Area Minimization," International Conference on Embedded Systems, pp. 899-906, January <u>2007</u>

# Outline

- 1. Overview of Process Defects

- 2. Definition of "Layout Sensitivity"

- 3. Statistical Layout Sensitivity Model

- 4. Application in VLSI design/verification process

- 5. Conclusions

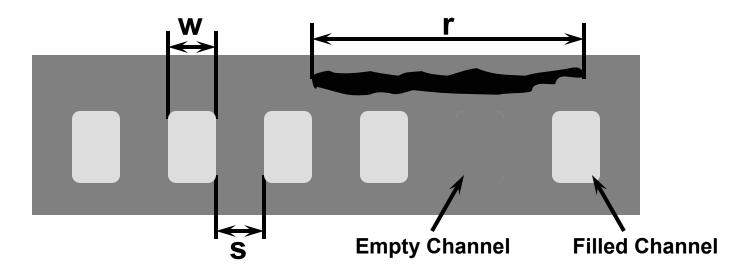

#### **Preliminary Analysis**

#### **Assumptions:**

- > Interconnects are placed on grids

- Layout is represented by a 1D system

- > Defect is approximated by a rectangle

# Our Goal:

#### Layout Sensitivity = Probability of Failure

### Definitions

- w Interconnect width

- **s** Interconnect spacing

- **r** Defect radius

- d Probability of filled channel

- **1-d** Probability of empty channel

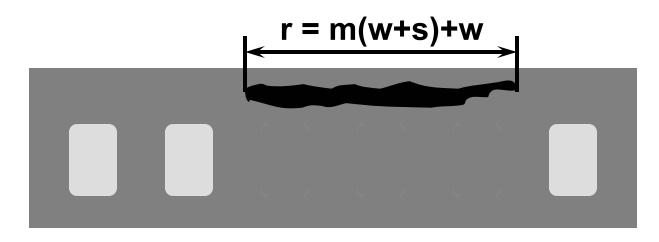

#### **Process Defects for Opens**

### Layout Sensitivity for Opens

- **Defect size**

- **Survival probability**

- Failure probability

- Layout Sensitivity

$$P_{s} = (1-d)^{m}$$

$P_f = 1 - (1-d)^m$

$$\mathbf{S}_{o} = \mathbf{1} - (\mathbf{1} - \mathbf{d})^{\frac{r-w}{w+s}}$$

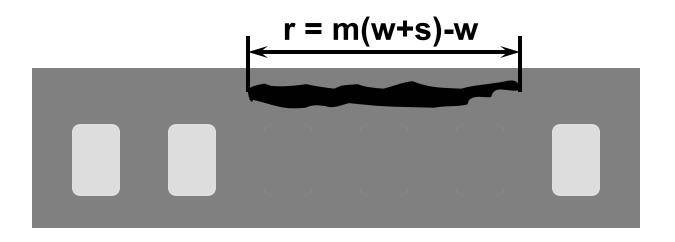

#### **Process Defects for Shorts**

March 17, 2007

Short defect

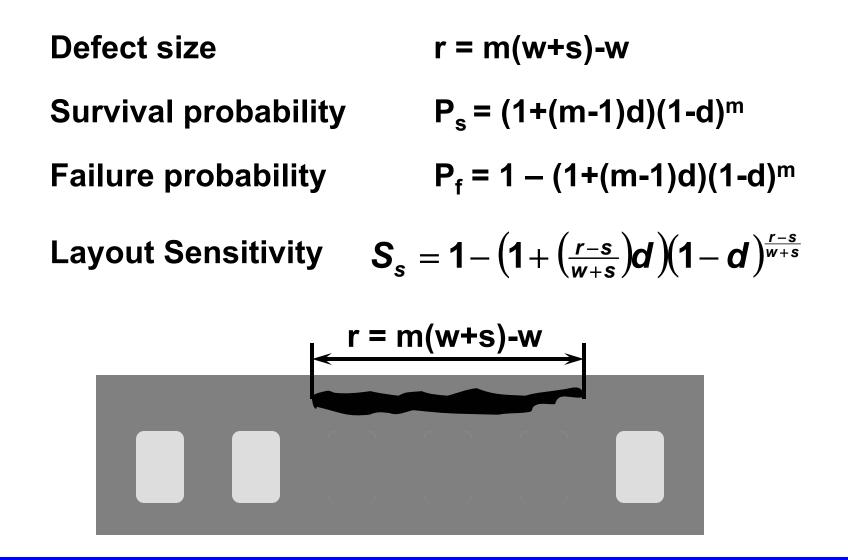

#### Layout Sensitivity for Shorts

**Defect size**

**Survival probability**

r = m(w+s)-w

$$P_s = (1-d)^m + m \cdot d \cdot (1-d)^{(m-1)}$$

m empty channel 1 filled and (m-1) empty channel

#### Layout Sensitivity for Shorts

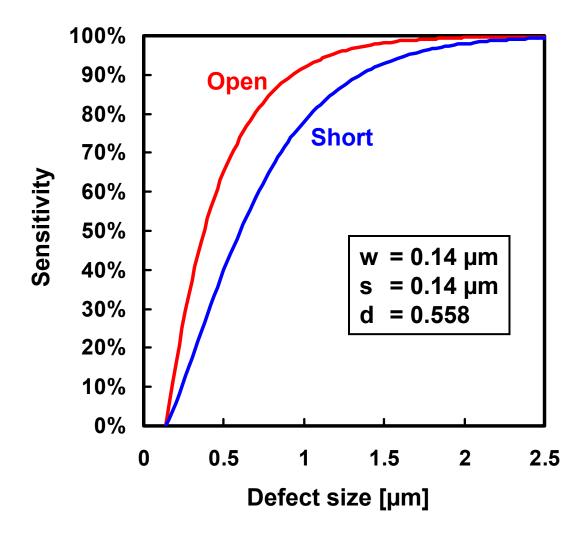

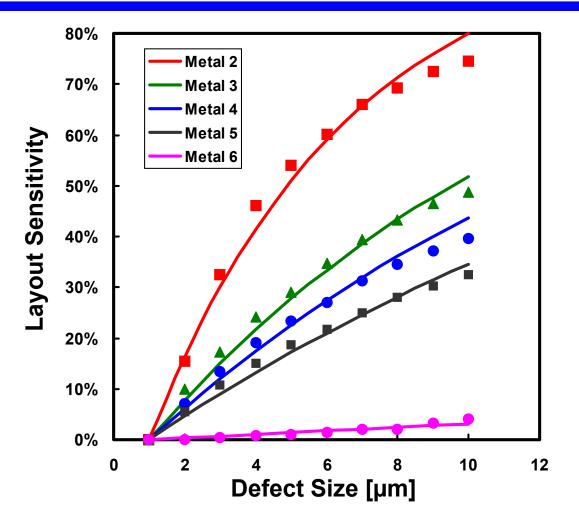

#### Layout Sensitivity versus Defect Size

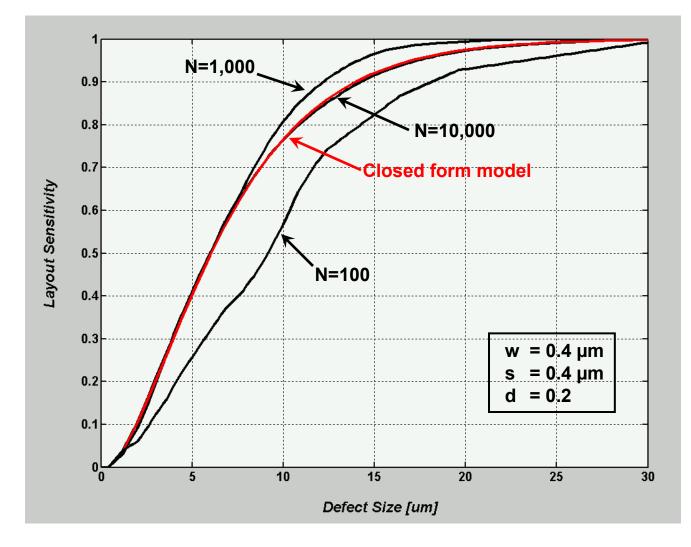

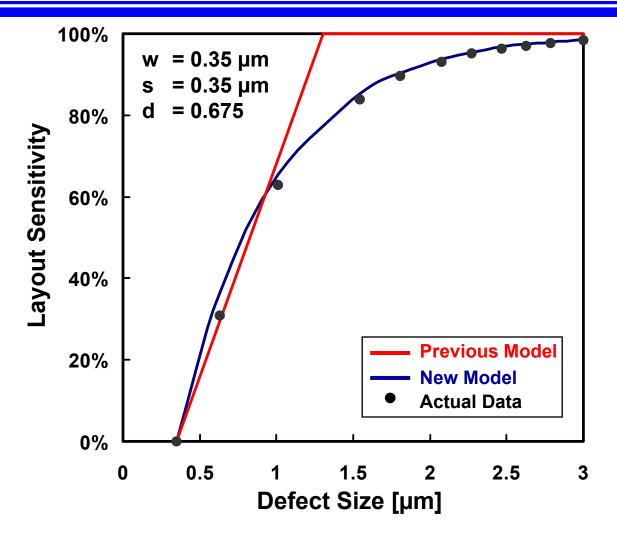

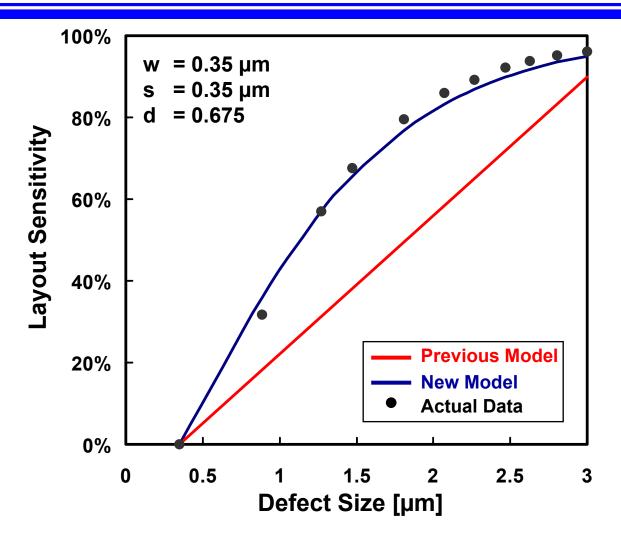

#### Mote-Carlo Simulation Results for Shorts

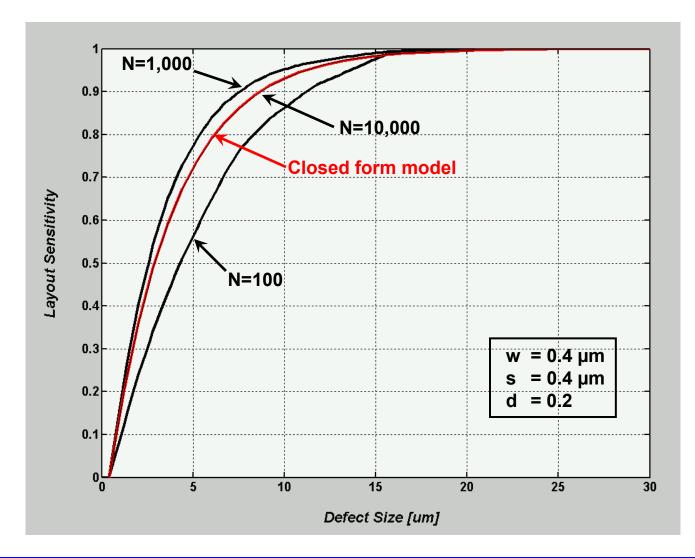

#### Mote-Carlo Simulation Results for Opens

#### Example for Opens in a Real Chip

Data from: J. Segal, L. Milor, and Y. Peng, "Reducing baseline defect density through modeling random defectlimiting yield," Micro Magazine, Jan 2000

# Outline

- 1. Overview of Process Defects

- 2. Definition of "Layout Sensitivity"

- 3. Statistical Layout Sensitivity Model

- 4. Application in VLSI design/verification process

- 5. Conclusions

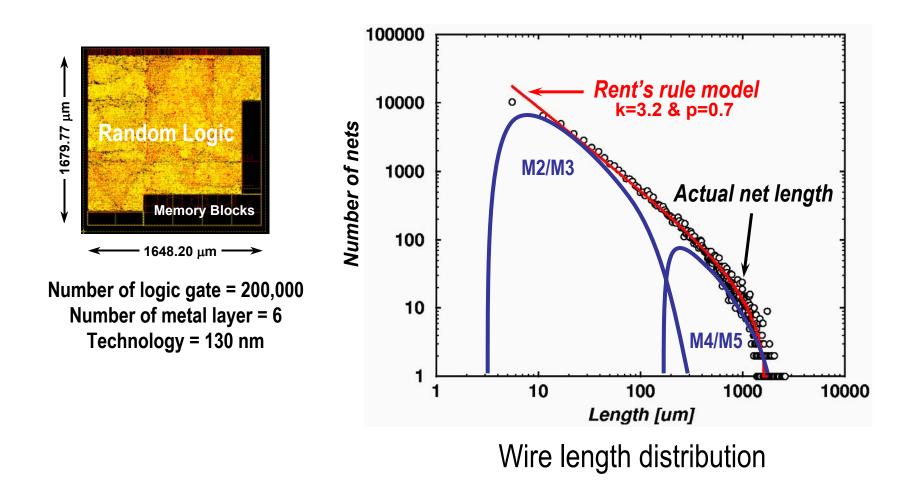

### **Application 1: Prediction of Layout Sensitivity**

H. Heineken and W. Maly, "Performance-Manufacturing Tradeoffs in IC Design," DATE 1998

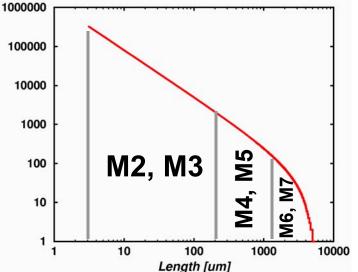

### Wire Length Distribution

### Prediction for 45nm Technology Node

Number of logic gate = 75 Million10Raw Gate Density = 854 KGate/mm²1

# of nets = 55.6 Million Gate Pitch = 1.14 um Chip size = 9.8 mm Average Length = 19.7 um Median Length = 2.2 um Total wire length = 1.37 Km

| Metal Layers | L <sub>min</sub> [μm] | L <sub>max</sub> [μm] | Ch. Density | % Net |

|--------------|-----------------------|-----------------------|-------------|-------|

| M2, M3       | 1.14                  | 102                   | 64 %        | 96 %  |

| M4, M5       | 102                   | 557                   | 52 %        | 3 %   |

| M6, M7       | 557                   | 5100                  | 26 %        | 1 %   |

### Example: New Layout Sensitivity for Opens

Data from: P. Christie and J. de Gyvez, "Pre-Layout Prediction of Interconnect Manufacturing," System Level Interconnect Prediction Workshop, pp. 167-173, March 2001

#### Example: New Layout Sensitivity for Shorts

Data from: P. Christie and J. de Gyvez, "Pre-Layout Prediction of Interconnect Manufacturing," System Level Interconnect Prediction Workshop, pp. 167-173, March 2001

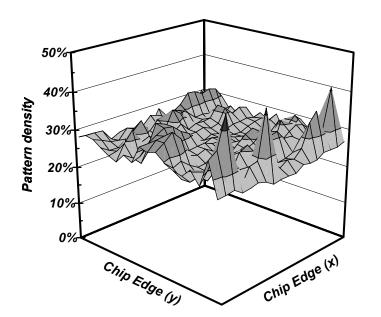

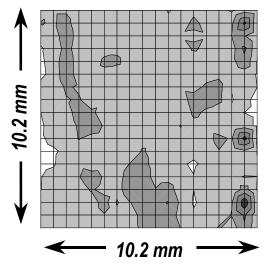

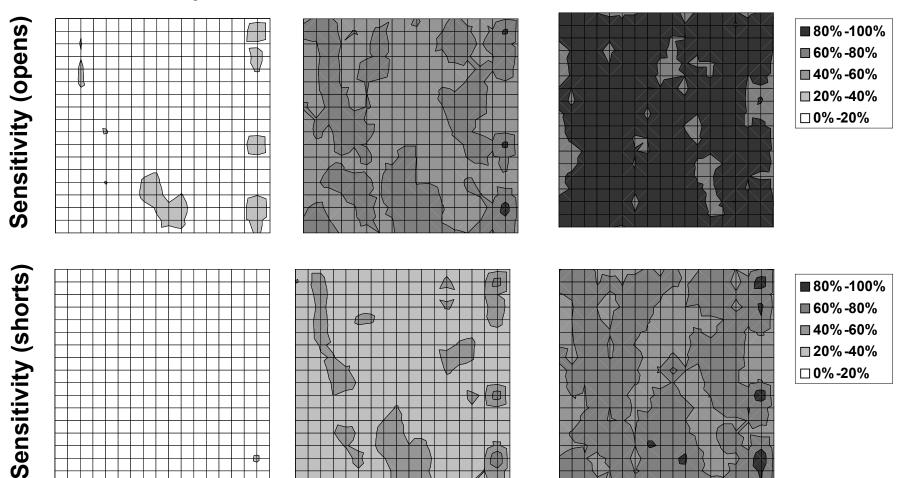

#### Application 2: Layout sensitivity Patterns

#### A 3-D Pattern Density Distribution

A 2-D Pattern Density Distribution

### Layout Sensitivity Patterns

r = 0.75 μm

r = 0.45 µm

#### r = 0.20 µm

#### Conclusions

- Layout sensitivity and critical area analysis has been around since 1982.

- Yield analysis and layout sensitivity is becoming more concern for modern VLSI designs. Critical area analysis is now part of design signoff process.

- Stochastic layout sensitivity model can expedite the yield analysis process significantly.

- Statistical modeling of layout sensitivity is just the beginning of many other applications for prediction of VLSI yield and manufacturability.